## YTLA-0220-2.0

Features:

Frequency:  $2\sim20GHz$

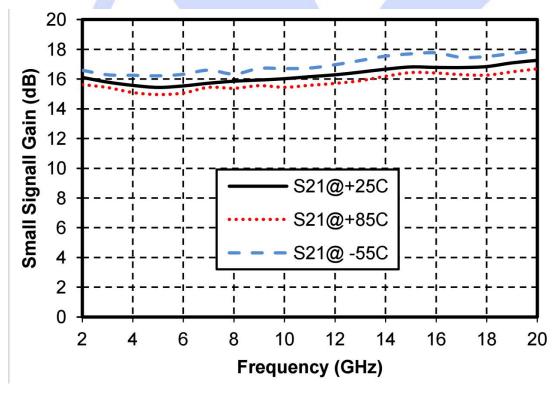

Small Signal: 16dB

Noise Figure: 2.0dB typ./3.5dB max.

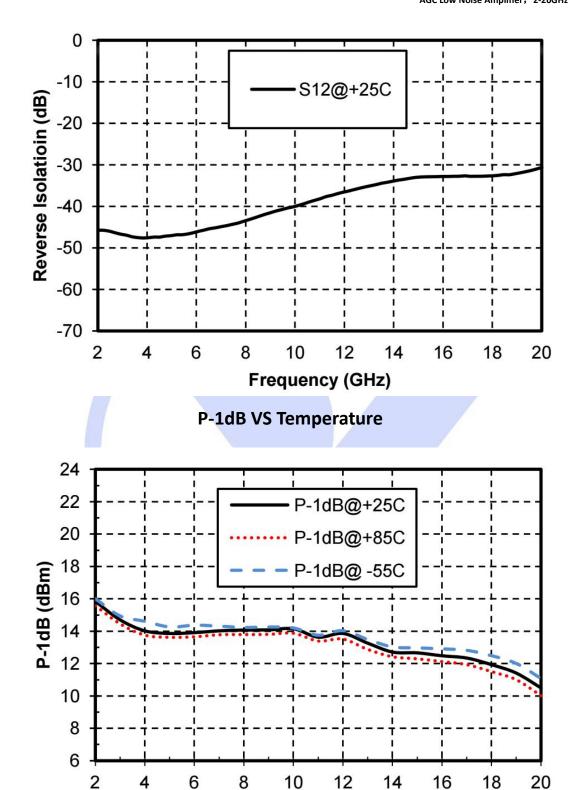

P-1dB: 13dBm

Supplying:+5V/50mA

PI.PO.:500hm

ISize: 2.5 x 1.6 x 0.1mm

**Description:**

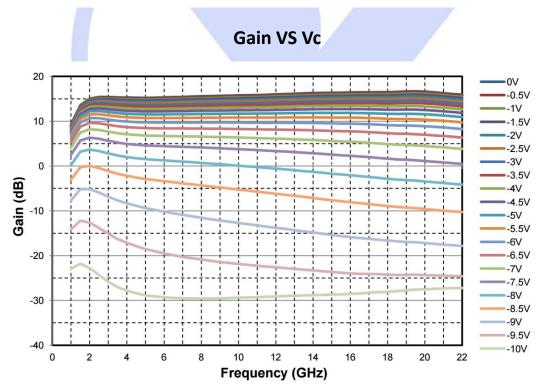

YTLA-0220-2.0 is a wideband low noise distributed amplifier with +5V supplying operation, and its frequency cover from 2-20GHz with small signal 16dB and P-1dB of 13dB as well as typical noise figure

2.0dB!Automatic gain control can be realized by tuning the terminal voltage of vc!The chip is back-metallized and can be die mounted with AuSn eutectic preforms or with electrically conductive epoxy.The mounting surface should be clean and flat.

| Limited Parameter   |              |  |  |

|---------------------|--------------|--|--|

| Max Drain Voltage   | 9V           |  |  |

| Max Input Power     | +18dBm       |  |  |

| Working Temperature | −55 ~ +85° C |  |  |

| Features           | Min   | Typical | Max   | Unite |

|--------------------|-------|---------|-------|-------|

| Frequency          | 2-20G |         |       | GHz   |

| Small Singal Grain | 15    | 16      | 17. 5 | dB    |

| Flatness           |       | ±1.0    |       | dB    |

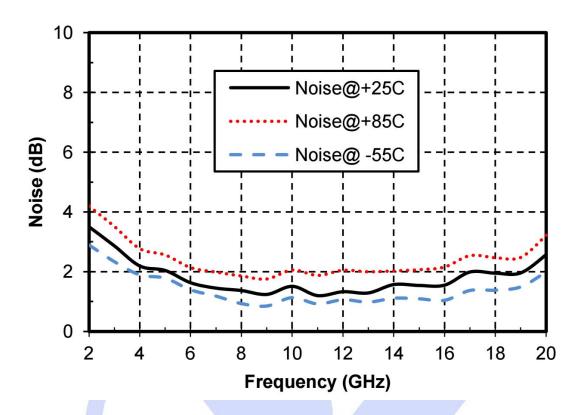

| Noise Figure       | _     | 2. 0    | 3. 5  | dB    |

| P-1dB              | 11    | 13      | 17.5  | dBm   |

| Psat               | 12. 5 | 14      | 20    | dBm   |

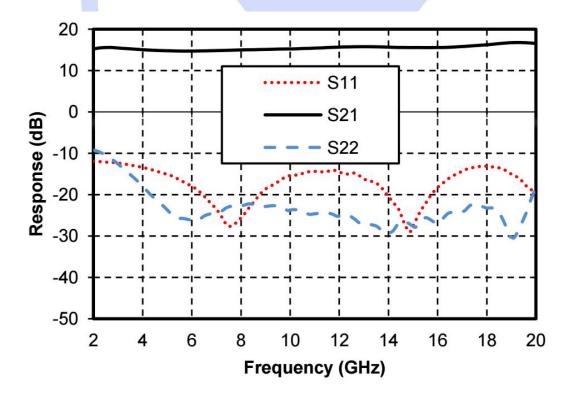

| Input Return Loss  |       | 16      |       | dB    |

| Output Return Loss |       | 14      |       | dB    |

| Static Current     |       | 50      |       | mA _  |

## **Gain VS Temperature**

**Noise Figure VS Frequency**

**Gain&Input/Output Return Loss VS Frequency**

**Isolation VS Frequency**

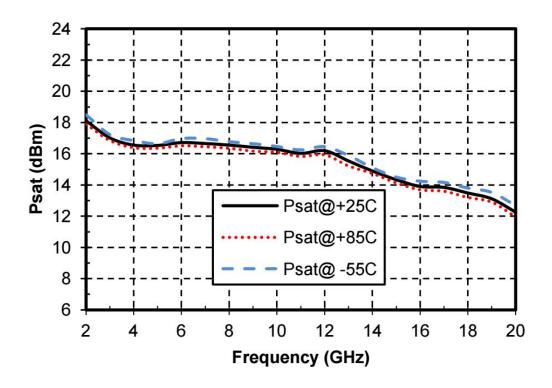

**Psat VS Temperature**

Frequency (GHz)

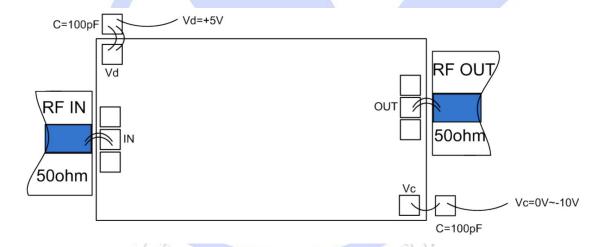

Outline Drawing:( µ m)

1600 3 Vd OUT 2 1050 450 1 IN Vc 4 150 2500

## **Assembly Diagram:**

## **Handling Precautions**

- 1.All bare die are placed in either Waffle or Gel based ESD protective containers, all die should be stored in a dry nitrogen environment.

- 2.Cleanliness: Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems

- 3. Follow ESD precautions to protect against ESD strikes

Handle the chip along the edges with a vacuum collet or with a sharp pair of bent tweezers. The surface of the chip has fragile air bridges and should not be touched with vacuum collet, tweezers, or fingers

4.Eutectic Die Attach: A 80/20 gold tin preform is recommended with a work surface temperature of 255 ° C and a tool temperature of 265 ° C. When hot 90/10 nitrogen/hydrogen gas is applied, tool tip temperature should

5.Epoxy Die Attach: Apply a minimum amount of epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip once it is placed into position. Cure epoxy per the manufacturer's schedule 6.Ball or wedge bond with 0.025mm (1 mil) diameter pure gold wire. Thermosonic wirebonding with a nominal stage temperature of 150 ° C and a ball bonding force of 40 to 50 grams or wedge bonding force of 18 to 22 grams is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds. Wirebonds should be started on the chip and terminated on the package or substrate. All bonds should be as short as possible <0.31mm (12 mils).